Journal of Engineering Research and Reports

20(8): 34-37, 2021; Article no.JERR.69118 ISSN: 2582-2926

# Substrate Design Augmentation for Die Placement Reference at Die Attach Process

Rennier Rodriguez<sup>1</sup>, Jr. Edwin Graycochea<sup>1\*</sup> and Frederick Ray Gomez<sup>1</sup>

<sup>1</sup>New Product Development and Introduction, Back-End Manufacturing and Technology STMicroelectronics, Inc., Calamba City, Laguna 4027. Philippines.

#### Authors' contributions

This work was carried out in co-operation amongst the authors. All authors read, reviewed and approved the final manuscript.

#### Article Information

DOI: 10.9734/JERR/2021/v20i817355 <u>Editor(s):</u> (1) Dr. Guang Yih Sheu, Chang-Jung Christian University, Taiwan. <u>Reviewers:</u> (1) Benisha M, Jeppiaar institute of Technology, India. (2) Anonymous, India. Complete Peer review History: <u>http://www.sdiarticle4.com/review-history/69118</u>

**Original Research Article**

Received 01 April 2021 Accepted 05 June 2021 Published 09 June 2021

### ABSTRACT

Die placement reference in die attach process is one of the critical aspects in measuring the actual die placement especially for the device that has a required measurement. This paper focused on the re-design on the layout of the substrate ball grid array (BGA) package with cross fiducials at the singulation lane which are located at the corner portions of the device. The cross fiducial would serve as a reference when measuring the actual placement of the Silicon die in the package. With this improvement, the technicians and operators could now easily identify the reference based on the mount and bonding diagram requirement.

Keywords: Die attach process; fiducial; pattern recognition; substrate design.

## **1. INTRODUCTION**

Semiconductors and electronics have become an integral part of our everyday activities. As

technology keeps on changing, we too must adapt to these changes. This is one of the biggest challenges for any semiconductor company to maintain its competitive market

\*Corresponding author: Email: edwin.graycocheajr@st.com;

position and value. Meeting the customer requirements is a priority top of any semiconductor manufacturing company. On the other hand, failures to provide customer expectation will result to possible business failure. Die attach is the process of attaching a semiconductor die either a lead frame or substrate carrier material. The process starts with picking the semiconductor die from a wafer Silicon tape. The most common method used in die bonding follows: first, the ejector needle pushes up the target semiconductor die from the wafer Silicon tape; second, the die is picked by a rubber tip or pick up tool; third, the die is placed and aligned with respect to the die paddle of the lead frame or substrate carrier material; and lastly, would be the standard die bonding techniques, bond force and ultrasonic. In this paper, a ball grid array (BGA) device is identified to be critical because of the die placement requirement of the product. Die placement reference is where the Silicon die edge refers to the measurement on the substrate to the center of cross fiducial.

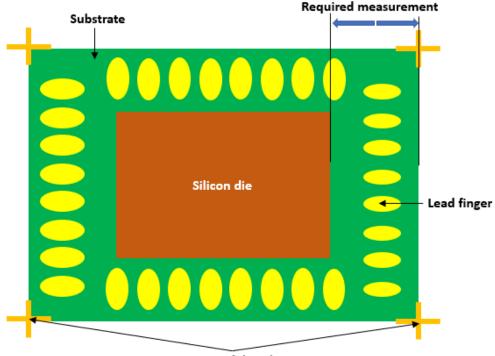

A recommended solution for this type of substrate is to have a cross fiducial visible on the substrate and to have a reference where the measurement is located. With this, die attach process is incorporated with a multiple of criteria such as die placement measurement, bond line thickness, and die tilt. The technician is required to perform a pre-buy off on the actual unit prior sending a good unit to be measured. Process control (PC) operator is one that measures the unit as a gating result prior to run the production lot. Fig. 1 shows the representation of a BGA device mount and bonding layout with a cross fiducial and required measurement on substrate.

#### 2. METHODS AND RESULTS

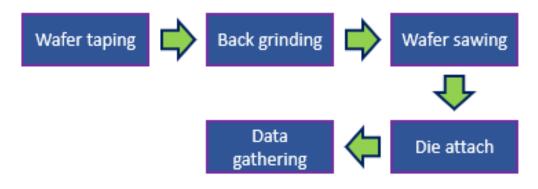

Cross fiducial is located at the corner areas of the individual unit, with each unit having four (4) cross fiducials. This cross fiducial serves as a reference especially for the machine pattern recognition or simply alignment. Works and studies related to the pattern recognition are shared in [1-5]. Fig. 2 shares the process data gathering method done on this study.

Cross fiducial

Fig. 1. BGA bonding layout

Rodriguez et al.; JERR, 20(8): 34-37, 2021; Article no.JERR.69118

Fig. 2. Process data gathering method

Wafer taping is a process where the Silicon wafer is taped active portion of the Silicon die. Next process is back grinding, this process uses a grinding wheel for thinning the required die thickness of the wafer. Wafer sawing is a process where the Silicon die is cut into individual pieces. Die attach process is responsible in picking the Silicon die to a wafer tape and bond to a substrate or leadframe carrier. After die attach process, data gathering was performed to see all the responses if this is pass or failed.

An improved substrate design with the cross fiducial is implemented for the device and this

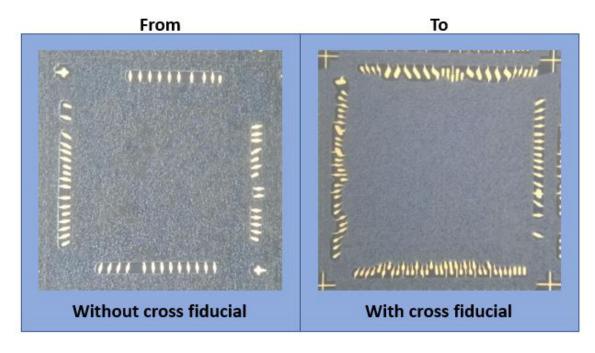

cross fiducial is critically important at die attach process station. With this solution, the technician or PC operator can easily identify where the die reference is located, unlike on the old design cross fiducial is not visible. One of the advantages of this solution is the pattern recognition of the machine because this is the accurate center of the whole unit, unlike on the old version of the substrate, the pattern recognition is placed at the lead finger. Fig. 3. shows the old substrate without cross fiducial and on the right side is the new substrate design with cross fiducial.

Fig. 3. Substrate design with cross fiducial

#### 3. CONCLUSION

This paper discussed a process design solution in modifying the substrate to have a cross fiducial on the corners of the die paddle. The cross fiducial is used as a reference guide during measuring the attached Silicon die on the substrate. For succeeding works and studies, this design could be used to process other devices with similar configuration or requirement. Moreover, studies and learnings shared in [6-10] are helpful to improve the die attach process.

#### DISCLAIMER

The company name used for this research is commonly and predominantly selected in our area of research and country. There is absolutely no conflict of interest between the authors and company because we do not intend to use this company as an avenue for any litigation but for the advancement of knowledge. Also, the research was not funded by the company rather it was funded by personal efforts of the authors.

#### ACKNOWLEDGEMENT

The authors would like to thank the New Product Development & Introduction (NPD-I) team and the Management Team for the great support.

#### **COMPETING INTERESTS**

Authors have declared that no competing interests exist.

#### REFERENCES

- Kim HT, et al. Automatic focus control for assembly alignment in a lens module process. 2009 IEEE International Symposium on Assembly and Manufacturing. South Korea. 2009;292-297.

- Salcedo MR et al. Enhanced die attach process defect recognition on QFN

leadframe packages. Journal of Engineering Research and Reports. 2021; 20(3);92-96.

- Freed M, et al. Autonomous on-wafer sensors for process modeling, diagnosis, and control. IEEE Transactions on Semiconductor Manufacturing. 2001;14(3); 255-264.

- 4. Gablan AG, et al. Improved die attribute recognition via colored glass wafer. Journal of Engineering Research and Reports. 2021;20(6);52-56.

- 5. Oh HW, et al. Gerber-character recognition system of auto-teaching program for PCB assembly machines. SICE 2004 Annual Conference. Japan. 2004;1;300-305.

- Buenviaje Jr. S, et al. Process optimization study on leadframe surface enhancements for delamination mitigation. IEEE 22nd Electronics Packaging Technology Conference (EPTC). Singapore. 2020;95-100.

- Chin LS, et al. Epoxy die attach challenges in miniature and compact DFN/QFN packages. IEEE 10th Electronics Packaging Technology Conference (EPTC). Singapore. 2008;475-480.

- Sumagpang Jr. A, et al. Introduction of reverse pyramid configuration with package construction characterization for die tilt resolution of highly sensitive multistacked dice sensor device. IEEE 22nd Electronics Packaging Technology Conference (EPTC). Singapore. 2020;140-146.

- Kahler J, et al. Pick-and-place silver sintering die attach of small-area chips. IEEE Transactions on Components, Packaging and Manufacturing Technology. 2012;2(2).

- Dinglasan J, et al. A robust approach of maintaining epoxy position on die attach process of tapeless QFN packages. Journal of Engineering Research and Reports. 2021;20(6);109-114.

© 2021 Rodriguez et al.; This is an Open Access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/4.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

> Peer-review history: The peer review history for this paper can be accessed here: http://www.sdiarticle4.com/review-history/69118